Доступна для скачивания новая версия vivado 2020.1

Содержание:

Step 6 : Enabling Cache Coherency in ZYQN

This is the most important information in this entire tutorial, so follow carefully. Let me explain a bit about why the cache coherency is needed in ZYNQ.

We have created and connected our IP core that it access the onboard DDR RAM. By default, ZYNQ PS also have direct access to onboard RAM. Now, since two parties use the same RAM, we have a shared memory. Coherency issue occurs due to the cache of ZYNQ PS. I will explain with an example.

Lets say ZYQN PS writes value of 0xFF in the memory address 0x000100 in our onboard RAM. This value will be in the cache of ZYNQ PS now. Now we trigger some operation in our IP core that overwrites the value in address 0x000100 to 0x11. When we try to read the result of the IP core from the ZYNQ PS, you will still see 0xFF in that memory location. Reason for this is no one informs the cache of ZYNQ PS that value in the memory location is updated from the PL side (our IP core is implemented in PL). Because of this you won’t be able to see any outputs from our IP core.

You can do few things to resolve this,

- Disable the data cache from the firmware/software in ZYNQ PS (Baremetal or Linux)

- Enforce cache coherency at the hardware level (Dosen’t depend on firmware/software)

First point can be achieved in Xilinx SDK if you are using baremetal mode, there is a seperate function for disabling data cache. But in Linux, there is no way to disable the data cache from the userspace. You have to write kernel space driver for this, which can be really hard for a beginner in Linux driver development.

Therefore second point can be the best solution, since it doesn’t depend on the software/firmware you use. But you will loose the ability of enabling and disabling cache at run time.

NOTE : If you don’t understand anything I said in this step of the tutorial, don’t worry. Just do as I say and everything will work.

Lets follow the second point and do the required changes in the hardware to enforce cache coherency.

In the block diagram, expand the S_AXI_ACP port on ZYNQ PS IP by clicking on the + sign. Now you will see side signals of AXI ACP port. According to the Xilinx documentation, we need to set following signals to 1 (HIGH) ,

- ARCACHE

- AWCACHE

- ARUSER

- AWUSER

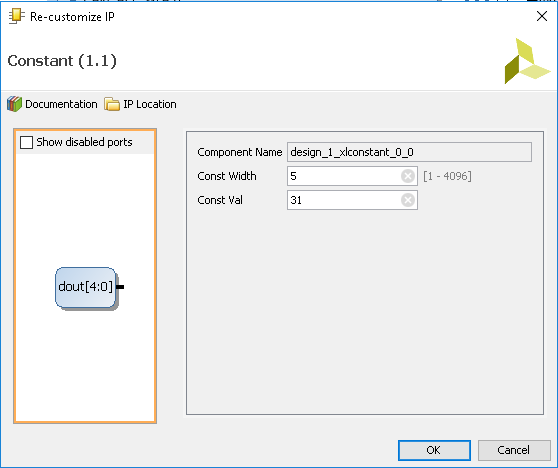

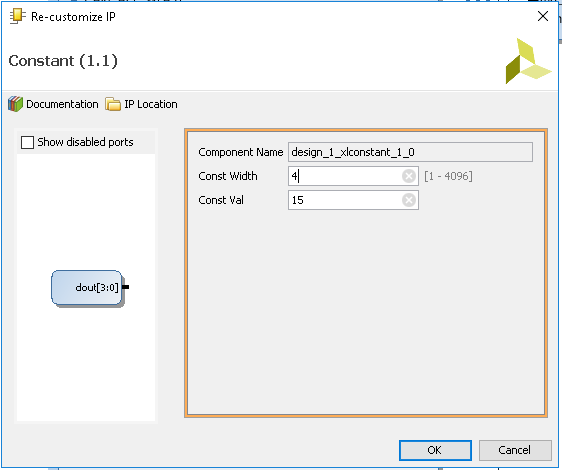

We will use constant block to override the values of these signals. Add two constant IP blocks to the design and configure them as below.

Configuration of constant IP block 1

Configuration of constant IP block 2

Solution

Older versions of some browsers have issues with file sizes greater than 4 GB.

Therefore, Xilinx requires the use of the Akamai Download Manager Java-based plug-in when downloading Vivado design tool images.

However, your company’s IT policy or firewall might not permit the Plug-in Manager to launch or operate properly.

To bypass the required Download Manager and attempt to download using your browser, click one of the following links:

Important Information: The following links are not recommended for use with any version of Internet Explorer prior to 9.

Internet Explorer 8 and earlier versions are known to have issues natively handling download files greater than 4 GB in size over an HTTP stream.

A Download Manager with start, stop, and retry capability is strongly recommended for the large Xilinx installation files.

Your browsers download capabilities alone might not be as robust or as fast as using a download manager.

Links for using browser download capability only:

Vivado Design Suite — HLx Editions — 2015.4 Full Product Installation

Windows: Vivado HLx and SDK Full Installer (TAR/GZIP — 8.9 GB) MD5 SUM Value: 2c6b1ff6f8d58b395f1c36cb96dc6551

Linux: Vivado HLx and SDK Full Installer (TAR/GZIP — 8.68 GB) MD5 SUM Value: d80076aabc744e453bf94c9186a638fd

All OS: Vivado HLx and SDK Full Installer (TAR/GZIP — 10.4 GB) MD5 SUM Value: dc41d22864175c41df0dd1b0c4556778

WebInstall Thin client Downloads

Linux 64: Vivado HLx 2015.4 WebInstall Thin Client (bin — 76.98 MB)MD5 SUM Value: c599ca2e5cae8721efc1841465a46fce

Windows 64: Vivado HLx 2015.4 WebInstall Thin Client (exe — 49.32 MB)MD5 SUM Value: cd91c8758f9ea474ad68ea794254c357

Linux 64: SDK standalone 2015.4 WebInstall Thin Client (bin — 76.92 MB)MD5 SUM Value: 2dac5f706427ad089a65335987adc628

Windows 64: SDK standalone 2015.4 WebInstall Thin Client (exe — 49.29 MB)MD5 SUM Value: 27a7f546c7732f1e58b979eee47d5b81

Vivado Lab Edition — 2015.4 Full Product Installation

Linux: Lab Installer (TAR/GZIP — 693.25 MB) MD5 SUM Value: 75bce66f7183d116bea864e536a9fb83

Windows: Lab Installer (TAR/GZIP — 665.14 MB) MD5 SUM Value: cb64c362aadc5edef8c64665c88a24af

Vivado Hardware Server — 2015.4 Full Product Installation

Windows: Vivado Hardware Server Installer (TAR/GZIP — 212.5 MB) MD5 SUM Value: 4028b49a74115ec1bb44a5a7b750b6da

Linux: Vivado Hardware Server Installer (TAR/GZIP — 185.03 MB) MD5 SUM Value: ad49f2376f4e204015df11a864f81619

Vivado 2015.4 Updates

Vivado 2015.4 Update 1 Image (TAR/GZIP — 1.14GB)MD5 SUM Value: d24fc9fdc5b91b6c9b4f2b5d45defdc4

Vivado 2015.4 Update 2 Image (TAR/GZIP — 1.2 GB)MD5 SUM Value: c8dd05289d8f950792eb86e77987d1ef

If you are still experiencing difficulties downloading the Xilinx Design Tools from the above links, as well as from our Download Center, please log into the Xilinx Technical Support page for further assistance.

Step 2 : Add ZYNQ PS to the Design and Configure

After you create the new project, select ‘Create Block Design’ option under Project Manager in to the right of the screen, as seen from the following figure. Put whatever name you want to the design in the pop-up window and click ok.

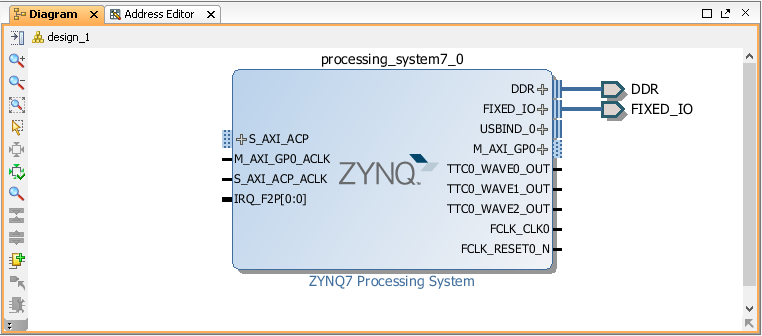

Click on ADD IP button in Block Design tool box and type in ‘zynq processing system’ and add that to the design by double clicking on it. As soon as IP added, there will be a Designer assistance prompt for “Run Block Automation”. Click on that, select OK on the pop-up window, it will add the board presets to the ZYNQ processing system IP. After running block automation, the IP will look like the following.

ZYNQ PS IP After running block automation

Now we need to configure the interfaces for interfacing our custom IP created by Vivado HLS in the previous tutorial. Before doing that lets remind few things about the custom IP we created in the previous tutorial. Our custom IP has the following interfaces,

- For data input and output : AXI Master (AXI Full) interface

- For configuring the IP at run-time : AXI Lite (slave) interface

We need to keeps these interfaces in mind when customizing ZYNQ PS. Since we have a AXI Full master port and AXI Lite slave port in our IP, we need an AXI Full slave and an AXI Lite master in the ZYNQ PS IP to connect our IP.

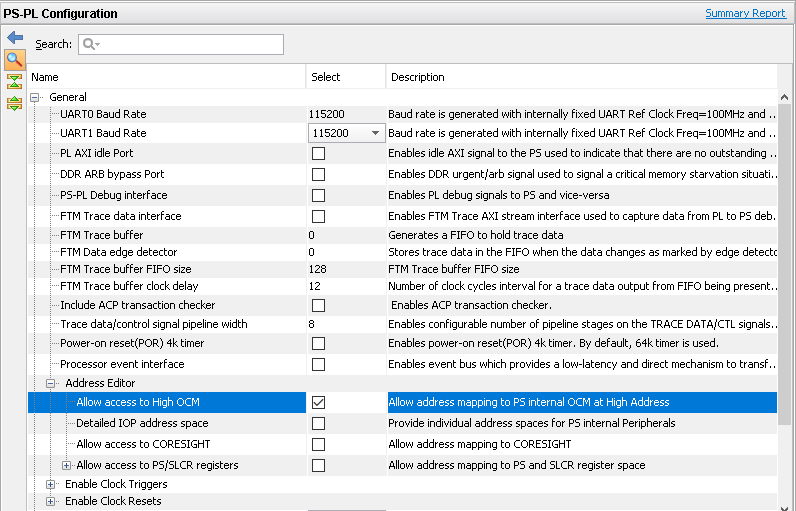

Now lets go ahead and customize the ZYNQ PS IP. To customize, double click on it. In the pop-up window select PS-PL Configuration in the Page Navigator. Then expand ACP Slave AXI Interface and tick both options under that, as in the following figure.

Enabling AXI ACP Port

Now we need to do something specific to Vivado 2015.4, which can be considered as a bug in this version. Go to General -> Address Editor and tick Allow access to High OCM, as shown from the figure. This option was enabled by default in previous version I used. If you don’t do this, you will get an error if you try to verify or elaborate.

Then go to Interrupts section in the page navigator and enable interrupts if you want them in your design. We actually don’t need interrupts for the IP we created, you can keep it disabled if you want. I mentioned it just for the completeness.

You can also change the clock frequency of the programmable logic (PL), that means the clock frequency of your custom IP. Following figure shows where you can find this option. I will keep the default clock configuration for now.

Clock Configuration

We are done customizing, click OK. ZYNQ PS IP should look like the following, after customizing.

Customized ZYNQ PS

Устанавливаем Vivado

Первым делом скачивай Vivado Design Suite — HLx Editions — 2018.2 Full Product Installation для своей ОС отсюда (на выбор варианты для Linux и для Windows).

Перед установкой следует зарегистрироваться на сайте.

Для ознакомительных целей я рекомендую установить бесплатную версию Vivado — WEB Pack, она по набору функций ничем не отличается от платной версии, но имеет ограничение на размер дизайна. Это значит, что счетчик в ней можно спроектировать, а что-то посложнее, что можно было бы продать, — вряд ли.

Программа установки Vivado 2018.2

В конце установки откроется Vivado License Manager, также его можно открыть и из Vivado — через вкладку Help в главном меню. Сюда нам нужно подсунуть файл лицензии. Давай создадим ее.

Скрин страницы http://www.xilinx.com/getlicense

- Заходим на xilinx.com, попадаем на следующую страницу.

- Выбираем свой аккаунт.

- Ставим галочку напротив Vivado Design Suite HL: WebPACK 2015 and Earlier License и жмем на Generate Node-Locked License.

- Далее используем MAC своей сетевой карты для идентификации хоста и генерируем файл лицензии, который ты позже получишь на почту.

- Получив файл лицензии в Vivado License Manager, жмем на Load Licence → Copy License.

Скрин Vivado License Manager на данном этапе

Теперь Vivado установлена, и нам нужно убедиться, что она корректно запускается.

Открываем терминал в Linux и пишем:

где — место установки Vivado. Теперь для запуска достаточно написать .

Также надо установить драйверы кабеля USB для загрузки прошивки. В Windows для этого просто ставим галочку Install Cable Drivers во время установки. В Linux следует вернуться в терминал и набрать следующее:

Теперь ставим драйверы для платы Zybo:

Запускаем пример и моделируем схему

Мы спроектируем четырехбитный бинарный счетчик с задаваемым направлением счета и выводом значения на светодиоды. Счетчик будет синхронным: работать он будет на одной тактовой частоте. При работе в железе счетчик станет изменять свое значение не каждый период тактовой частоты, а один раз в секунду, иначе мы не увидим моргание (при частоте 125 МГц оно для глаза сольется в ровный свет).

После загрузки проекта в FPGA он будет работать так: каждую секунду четыре светодиода переключаются в соответствии с бинарным представлением значения счетчика. Помимо светодиодов, на плате есть еще кнопки и тумблеры. При нажатии на одну кнопку счетчик сбрасывается в ноль. Один из тумблеров разрешает счет, второй тумблер — задает направление счета.

Чтобы получить исходный код и запустить проект в Linux, нам нужно ввести такие команды:

В Windows в месте выполнения скрипта надо открыть специальное терминальное окно из меню «Пуск» и из папки, созданной во время установки Vivado, перейти в директорию , где выполнить команду из файла .

В терминале открывается Vivado, создает проект, добавляет в него исходные файлы. Далее открывается Vivado TCL shell, здесь вводим команду , чтобы перейти в режим GUI. В окне Flow Navigator жмем Simulation → Run Simulation → Run Behavioral Simulation и видим окно вейвформ сигналов.

Вейвформы сигналов при моделировании

В этом окне отображаются зависимости от времени логических сигналов внутри нашей схемы счетчика. Мы видим тактовый сигнал , сигнал сброса , сигнал разрешения работы , сигнал выбора направления счета , сигнал , который определяет частоту переключения битов счетчика, и, наконец, значение счетчика, выведенное на четыре светодиода.

Самое время посмотреть на исходные файлы! Закрываем симуляцию и смотрим в окно Sources.

Исходные файлы проекта

В разделе Design Sources лежат исходные файлы RTL на языке System Verilog: и . В каждом определено по одноименному модулю, причем, как видно, модуль находится внутри модуля , что определяет иерархию модулей проекта.

В разделе Constraints находятся файлы ограничений XDC (Xilinx Design Constraints). Как уже упоминалось, в них определяются ножки микросхемы, к которым должны подключаться порты ввода-вывода верхнего уровня RTL (top level) и период тактового сигнала.

В разделе Simulation Sources, помимо наших файлов RTL, мы видим еще один уровень иерархии — самый верхний. Это так называемый (tb) — виртуальный стенд, куда мы поместили модуль

Надо обратить внимание, что модуль не имеет портов ввода-вывода: входные сигналы для нашей схемы назначаются непосредственно средствами языка System Verilog

Посмотрим на код .

Вариант 1. Присоединись к сообществу «Xakep.ru», чтобы читать все материалы на сайте

Членство в сообществе в течение указанного срока откроет тебе доступ ко ВСЕМ материалам «Хакера», увеличит личную накопительную скидку и позволит накапливать профессиональный рейтинг Xakep Score!

Подробнее

Вариант 2. Открой один материал

Заинтересовала статья, но нет возможности стать членом клуба «Xakep.ru»? Тогда этот вариант для тебя!

Обрати внимание: этот способ подходит только для статей, опубликованных более двух месяцев назад.

Я уже участник «Xakep.ru»

Что нового?

Установка и лицензирование

- Поддержка проверки загрузки (Digest и Signature)

- Загрузка определенного типа ПО при использовании Web Installer

- Загрузка полного пакета ПО

- Загрузка определённого ПО

Улучшения среды

- Новые примеры проектов и утилита загрузки файлов поддержки отладочных плат. Загрузка только выбранных и необходимых файлов для отладочных плат компании Xilinx и сторонних производителей с github

- Загрузка новых и улучшенных примеров проектов

IP интегратор

- Внедрены новые концепции “Path” и “Network”

- Полный кросспробинг в Address Editor

- Подсвечивание ошибок в реальном времени

- Новая панель “Address Path”

- Новое представление/перспектива “Addressing View”

Расширение функционала IP ядер

Дата центры

- Расширение функционала ERNIC

- Новое AES IP для приложений криптографии

- Новый NVMe Target Controller IP, подключаемых к хост-ускорителю для хранения данных

- Доступен NVMeOF turnkey U50 Alveo. Включая FPGA битфайл и документацию

- Улучшенная ревизия Queue DMA Subsystem для PCI Express (QDMA 4.0) — улучшены тайминги, уменьшено количество занимаемых ресурсов, упрощен процесс миграции

IP для проводной/беспроводной передачи данных

- Добавлена поддержка JESD204C для GTH3/4 — предварительны релиз 2020.1

- Новый ORAN Radio Interface IP, обеспечивающий O-RU (O-RAN radio unit) функционал с добавленным специализированным SRS/PRACH AXI-stream и 32 spatial streams

- Новое 400G FEC IP

- В AXI Ethernet добавлена поддержка переключения между SGMII и 1000BASE-X

- В 50G Ethernet Subsystem добавлен опциональный программный 50G ‘KP2’ NRZ FEC

- Для интегрированной 100G Ethernet Subsystem добавлен опциональный программный 100G ‘KP4’ NRZ FEC

Базовые IP

- Firewall IP — защищает либо восходящее, либо нисходящее направление. Это IP помогает изолировать регионы в FPGA-as-a-Service и других приложениях

- SmartConnect IP оптимизирован для режима минимальной площади, а также для режима 1×1

IP для работы с видео и изображениями

- В SDI Subsystem добавлена поддержка 12bpc и HFR

- В MIPI CSI Transmit subsystem доавлена поддержка цветовых форматов raw16 и raw20

- В Video mixer добавлена опция выбора колорометрии BT.709 и BT.601

- В HDMI2.0 Subsystems добавлена поддержка 32 каналов аудио и 3D аудио

Синтез

- Возможность переопределения атрибутов HDL с помощью ограничений XDC позволяет изменять поведение синтеза без изменения исходного кода HDL.

- Повторное использование и интеграция проектов из разных языков с улучшенной передачей параметров между различными языками в одном проекте

- Производительность значительно повышена при обработке вызовов функций. Улучшения были сделаны для всех языков

- Новая директива под названием Logic Compaction реализует арифметические функции с меньшей точностью, используя минимальные логические ресурсы.

- Сопоставление памяти значительно улучшено за счет балансировки массивов по различным типам ресурсов, чтобы избежать высокого использования определенного типа ресурсов.

Имплементация

Dynamic Function eXchange (DFX)?

- Вложенный DFX позволяет пользователям размещать одну или несколько динамических областей внутри динамической области для дальнейшего расширения гибкости DFX

- Преимущества

- Упрощённая верификация

- Более мелкая «зернистость»

- Все существующие IP для частичной реконфигурации (Partial Reconfiguration) были заменены эквивалентными IP с терминологией DFX

Маршрут проектирования — этап Имплементации

- Pblock теперь по умолчанию типа SOFT

- Единственное исключение: блоки DFX Pblocks имеют жесткие границы по определению и не могут стать SOFT

- Размещение ячеек вне границ Pblock может улучшить производительность

Анализ проекта и сходимость временных характеристик

- Отчет QoR Suggestions прогнозирует до 3 пользовательских стратегий для повышения производительности

- Прогнозируется, что он даст лучшие результаты, чем Default и Performance_Explore

- Экономит время компиляции и уровень «стараний» для проверки многих стратегий

- Запустите report_qor_assessment (RQA), чтобы проверить, совместим ли проект с прогнозом стратегии.

- отчет report_ram_utilization был полностью переработан для предоставления соответствующей информации

- Поиск компромисса по ресурсам памяти

- Выявление неэффективных DRAM

- См. раздел оптимизация post opt

- Факторы, Ограничивающие Производительность / Мощность

Анализ энергозатрат

- Vivado теперь генерирует отчет по шинопроводу

- Отчёт по шинопроводу теперь доступен для Alveo U50

Vivado 2020.1Vitis/Vivado тренинг центраКоробковМихаил m.korobkov@inline-ctc.ru+7-495-797-61-74 (доб 237)

Vivado 工具

-

- 增加了对基于命令行的 Web 安装程序的支持,从而提高了安装 Xilinx 工具的用户体验和工作效率

- 支持磁盘使用优化,可减少安装 Vivado 工具的空间占用

- Xilinx 已停止提供 Vivado 工具 DVD

-

- 2 个最新超高采样率 (SSR) 块:将向量断言及向量关系块添加至 Xilinx SSR 块库,用于为 Zynq UltraScale+ RFSoC 部件等 Xilinx 器件构建超高采样率 (SSR) 设计。如欲了解有关超高采样率设计及最新模块库的更多详情,请参阅用户指南。

- 所支持的 MATLAB 版本:R2018a、R2018b 和 R2019

-

- 可将 C 语言函数标记为黑箱,替换为用户提供的等效 RTL 模块

- 数据流适用范围现在可扩展,以通过最新“稳定的”pragma/directive 支持一个阵列的多个读取器

- 可通过数据流 pragma/directive 指定一个数据流交替缓冲序列,以提高并行执行能力

- 修改后的内存资源 pragma/directive 允许指定存储类型及时延

- 用户可将 ap_ctrl_none 范围设置为数据流区域,以提高吞吐量

- C 库

- C++ 模板化超高采样率 (SSR) FFT 函数。脉动阵列架构,支持每个时钟周期的多个数据采样(整数或定点)

- 通过 xfOpenCV 增强 OpenCV 支持(版本说明)

- 全面的 math.h 函数集现针对定点数据类型进行了本地优化

-

- 增加了 VHDL-2008 特性,包括数据包通用术语、字符实体通用类型和通用函数。

- 增量综合现已提供,可为 Vivado 项目提供可选自动增量模式。

-

- DSP 模块库: 最新 FFT、IFFT 和 FIR 块现在可使用 Model Composer 来设计和实现信号处理算法

- 吞吐量控制的增强功能:支持吞吐量控制的块阵容更强大。使用支持的块构建设计并控制实现方案的吞吐量需求,无需对设计进行任何结构修改

- 支持流媒体数据的其它模块:使用支持流媒体数据运行的更广泛块集设计和实现具有高吞吐量需求的算法。示例:查找表、延迟、矩阵乘法和子矩阵等。

- C/C++ 函数导入过程中的增强复杂性支持:除了 std::complex 之外,还增加了对导入函数(使用 hls::x_complex 类型)的支持,从而在自定义块中扩展了对复杂信号的支持。

- C/C++ 函数导入的增强功能:使用 xmcImportFunction 特性为您的设计创建自定义“源”块

- 增强了对行矩阵及列矩阵信号维数的支持:改进代码生成基础架构,在设计中处理行矩阵 和列矩阵 信号,从而提高性能。

- 支持的 MATLAB 版本:R2018a、R2018b 和 R2019a

-

- 自动向项目摘要仪表板添加新运行

- 能够‘保存为’报告策略

-

只需在 GUI 中单击一下,就可直接从 Github 下载并安装第三方电路板

-

- 引入对 SystemVerilog 功能覆盖和报告生成(.txt 或 .html)的支持

- 支持对并发区域中的属性和序列进行断言

- 增强的约束随机化 supportNew 协议实例窗口,可在设计中显示 AXI 接口

- 方框图中的“Mark Simulation”特性,可直接在波形查看器中添加 AXI 接口

-

- 设计中的加密块将隐藏在原理图和层级查看器中。引入了适当的最新 xilinx_schematic_visibility,其可通过切换开关来修改默认行为

- 更新的 Xilinx Vivado 公开密钥,可作为定期安全更新的一部分

-

- 最新 AXI Regslice IP 可高速通过 SLR,自动插入流水线。

- 提高 Virtex UltraScale+ HBM 设计性能(高达 450 MHz)。

- 支持所有 UltraScale 和 UltraScale+ 器件。

- 基于属性的机制,可用于自定义总线及接口。

- 布置过程中,高扇出网的物理优化更快。

- 自动 SLR 交叉寄存器的使用,可提高性能,减少 QoR 变化

- 对于带有许多时序异常的设计,报告方法的运行速度可提高 2 倍。

- opt_design 添加一个 SRL remap 选项,可在 SRL 位移寄存器原语和寄存器链之间转换。允许平衡利用率和性能。

- 最新 AXI Regslice IP 可高速通过 SLR,自动插入流水线。

-

- 软 Pblock:可使 Pblock 边界变软,允许各单元按要求移动,以提升性能。

- SLR Pblock:现在可使用 SLR 指定 Pblock 范围,以实现更简单的定义。

- report_methodology 命令可添加与时序相关的新方法检查。

- report_qor_suggestions (RQS) 的建议现在是基于对象的,由实现流程命令自动应用。

- 重新构建 report_ram_utilization 命令,可为稀疏性及时序临界性提供更有意义的统计信息。

-

- UltraScale+ XPE 包含更详细的 RF 数据转换器设置,用于 Zynq UltraScale+ RFSoC Gen 3 器件的功耗分析。

- UltraScale+ XPE 添加一个 HBM 向导,为 HBM 功耗分析提供系统级参数输入,以便自动生成相应的电子表格条目。

-

- IBERT GTM:在 GTM 及串行 I/O 分析仪的 IBERT 设计中,可使用 PAM4 和 NRZ 调制为 GTM 收发器实现 9.8 Gb/s 的线路速率,最高可达 58 Gb/s。支持 PAM4 信令的正向纠错 (FEC) 模式以 160 位数据位宽模式和内部 PRBS 模式提供(FEC 不支持 NRZ)。此外,还为眼交叉分析筛选器、直方图和不同链接的信噪比信息提供新的绘图功能。

- Busplot Viewer:逻辑分析仪现在为调试 DSP 和 RF 应用提供 Busplot Viewer 功能。这允许用户根据探针值、时间或样本以及其它探针数据绘制不同的图表。查看器允许用户选择任何信号,用作 X 轴和 Y 轴数据,在同一图上绘制多个图形。

- HBM Monitor:全新内存调试功能可用于监控 HBM 设计状态及性能。与内存校准调试类似,HBM 监控器仪表板将显示 HBM 内存模块的校准状态和静态温度,以及各种吞吐量信息和不同通道上的监控活动。

- RF Analyzer:用于调试 ZU+ RFSoC 器件的 RF 分析仪工具现已提供。该工具主要用在用户电路板上,帮助了解电路板在高频率应用中的性能。RF 分析仪将相同的基本 GUI 用作 RFSoC 评估工具。RF 分析仪虽然提供大量类似的特性,但与电路板无关。RF 分析仪无需使用特定电路板实现信息,依赖 BRAM 缓冲器,而不是 DDR RAM,电路板需要时,可要求用户配置一个外部锁相环,并可通过 JTAG 在主机 PC 和目标电路板之间通信。

-

- 最新 50G RS-FEC(544、514):用于 5G 无线应用的最新 FEC (2x26G) NRZ,在添加外部 bitmux 芯片时,可实现 PAM-4 应用

- 集成型 UltraScale/UltraScale+ 100G 以太网子系统:全新可选 AXI 数据总线接口支持基于标准的接口

- 10G/25G 以太网子系统、40G/50G 以太网子系统、集成型 UltraScale/UltraScale+ 100G 以太网子系统、USXGMII、1G/10G/25G 以太网交换子系统:通过基于所选特性创建统计逻辑,实现尺寸优化的统计计数器

- 视频与影像 IP:视频处理内核新增对 8K30 分辨率的支持,视频混频器增加 16 层混合,而帧缓冲器则新增对 12 和 16bpc 的支持;

- SmartConnect: 提高了面积效率、特别适合小型配置和 AXILite 端点

- AXI Bram 控制器:改善了单拍事务处理的性能。可配置的读取时延,适用于紧密的时间间隔。

Step 7 : Synthesize and implement the design

First validate the design once to make sure all the connections are correct. Once you confirm that the validation is successful. We need to create a HDL wrapper for our block design before synthesizing. Right click one the design name in the sources tab as below and select Create HDL Wrapper. Tick “Let Vivado manage wrapper and auto-update” and click OK.

Creating HDL wrapper

Let’s proceed to synthesize the design. You can do this step by step ( RTL simulation -> Elaboration -> Synthesis -> Bit stream generation ), analyzing the results of each step. But I will skip the RTL simulation and run the whole thing by clicking Generate Bitstream. Vivado will say that there are no previous results available and ask to run previous steps as well. Select Yes and it will start the process.

After synthesis finishes successfully (this will need a valid license ofcourse ), you can export the implemented hardware to be used in Xilinx SDK. Next tutorial will be focused on running our design on the Xilinx ZC702 board itself using Xilinx SDK in baremetal mode.

You can find the source of the Vivado project in this repo.

Имплементация

-

Dynamic Function eXchange (DFX)

- Частичная реконфигурация (Partial Reconfiguration (PR)) является частью общего решения DFX

- DFX включает: возможности устройств, маршруты проектирования в Vivado, IP для частичной реконфигурации и многое другое

- Распространяется на все архитектуры: от 7-ой серии до Versal

- Новый функционал в будущих релизах

- Читайте подробнее здесь

- AXI High-Bandwidth ICAP interface IP

- Поддержка чтения и записи по AXI до 256 пакетов за транзакцию

- Дополнительный интерфейс мастер AXI4-Stream для чтения с неограниченной длиной пакета за транзакцию

- Memory mapped AXI4 слэйв интерфейс

- Поддержка записи и чтения размером до 230 байт?

- Подробнее в PG349

- Частичная реконфигурация (Partial Reconfiguration (PR)) является частью общего решения DFX

-

Этап имплементации

- Опция PhysOpt теперь включена по умолчанию в стратегии Vivado Implementation Defaults

- Новая директива Default опции phys_opt

- Меньше оптимизированных путей, чем в предыдущих версиях?

- Сосредоточена на решении временных выбросов

- Очень быстрое выполнение

- LUT combining optimization добавлена в «Physical-Synthesis-in-Placer» (PSIP)?

- Новая оптимизация для путей, содержащих BUFG/CE в опции opt_design

-

Анализ и достижение заданных временных ограничений проекта

- Стратегия предсказания RQS (report qor (Quality of results) suggestions)

- Использует ИИ для предсказания 3-х лучших стратегий имплементации

- report_qor_suggestions -strategy

- RQA (report_qor_assessment)?

- Содержит рекомендации по использованию стратегий инкрементной компиляции и стратегии имплементации RQS

- Добавляет сводку report_failfast для отслеживания проблем проектирования перед импелементацией?

- Новая метрика перегруженности: добавлена визуализация уровня перегрузки соединений (Windows -> Metrics)?

- Команда report_ram_utilization дополнена отчётом о LUTRAM

- Новая UltraFast методология для проверки небезопасных путей пересечения тактовых доменов (CDC) между MMCM

- Стратегия предсказания RQS (report qor (Quality of results) suggestions)

-

Инкрементная компиляция

- Дерективы инкрементной имплементации

- Quick: самое быстрое выполнение, минимальные усилия достижения временных ограничений

- RuntimeOptimized: быстрое выполнение при сохранении временных ограничений

- TimingClosure: пытается достичь временных ограничений

- Не нужно изменять директивы размещения и трассировки

- Улучшены результаты, достигаемые с помощью опции phys_opt_design при инкрементной имплементации

- Более точная оптимизация

- Улучшено переиспользование предыдущих результатов размещения и трассировки

- Инкрементный синтез: повторное использование предыдущих результатов теперь учитывает изменения в параметрах synth_design

- Дерективы инкрементной имплементации

Step 5 : Setting address spaces

Since we are using AXI M Full interface in our IP core, each memory address that our IP core access, is mapped into a specific address in ZYNQ SoC (This is because AXI M i a memory mapped interface). This is a common way that is used to control the peripheral connected to a processor.

Now we have to decide what address range of ZYNQ PS will be mapped in to each port of our IP core. In my next tutorial, I will discuss how we are controlling our IP core from the Linux installed on ZYNQ PS by accessing these mapped memories.

When designing our IP core, I have bundled all control signals (AXI Lite signals) of the IP core to a bundle named “CRTL_BUS”. And I have configured the AXI M interfaces such that we can set the address of these memory mapped ports at the run time using a AXI Lite control signal, which is also bundled to CRTL_BUS.

Go to Address Editor in the block diagram window, expand the entries and you will see something like below.

Address space before change

Correct these address spaces as below, some required address spaces are excluded by default due to a bug in this Vivado version. Unmap all ports under conv_0 IP core and map and include only the two ports as below.

Updated Address Spaces

Click on Validate design button just to check whether all is correct. Validation should be successful before you proceed.

Model Composer

- Улучшена поддержка работы с векторами сигналов: улучшение в генерации кода для управления векторами из сигналов, приводящая к повышению производительности.

- Усовершенствование блока Constant для параметров, заданных в виде вектора: блок Constant теперь поддерживает интерпретацию параметров, заданных в виде одномерного вектора, аналогично как блок Constant в Simulink

-

Новые примеры проектов с оптимизацией DSP блоков:

- Реконструкция изображений МРТ при использовании 2D-БПФ

- Разработка низкочастотного фильтра с использованием блока FIR

- Сглаживающий фильтр изображения с использованием блока FIR

- Улучшение экспорта С/С++ функций: улучшен вывод сообщений об ошибках в окне Diagnostic Viewer

- Настройка свойств IP блоков для их экспорта в IP каталог: доступно указание свойств экспортируемого IP: имя. версия, язык (VHDL или Verilog)

- Поиск целевого устройства в Devise Chooser: быстрый поиск целевого устройства или платы по множеству критериев

- FIR блок поддерживает многоканальную обработку: поддержка обработки столбцов входящего сигнала в качестве независимых каналов данных для операций многоканальной фильтрации

- Поддерживаемые версии Matlab: R2018a, R2018b, R2019a и R2019b